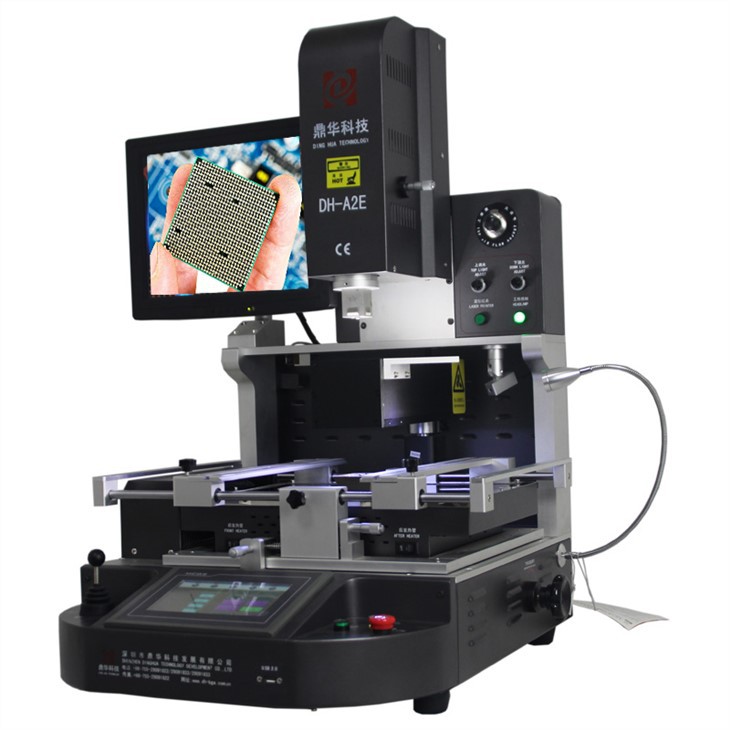

Auto Optical BGA Rework Station

Χρησιμοποιείται ευρέως στην επισκευή σε επίπεδο chip για μητρική πλακέτα κινητού, φορητού υπολογιστή, υπολογιστή, τηλεόρασης, κλιματιστικού κ.λπ. Έχει υψηλό ποσοστό επιτυχίας επισκευής και υψηλό βαθμό αυτοματισμού και εξοικονομεί πολλές ανθρώπινες προσπάθειες. Είμαστε επαγγελματίες κατασκευαστές αυτού του μηχανήματος και διαθέτουμε αυτά τα μηχανήματα σε απόθεμα.

Περιγραφή

Auto Optical BGA Rework Station

1.Εφαρμογή Auto Optical BGA Rework Station

Μητρική πλακέτα υπολογιστή, έξυπνο τηλέφωνο, φορητός υπολογιστής, πλακέτα λογικής MacBook, ψηφιακή κάμερα, κλιματιστικό, τηλεόραση και άλλα ηλεκτρονικά

εξοπλισμοί από ιατρική βιομηχανία, βιομηχανία επικοινωνιών, αυτοκινητοβιομηχανία κ.λπ.

Κατάλληλο για διαφορετικά είδη τσιπ: BGA, PGA, POP, BQFP, QFN, SOT223, PLCC, TQFP, TDFN, TSOP, PBGA, CPGA, τσιπ LED.

2. Χαρακτηριστικά προϊόντος του Auto Optical BGA Rework Station

•Υψηλό ποσοστό επιτυχίας επισκευής σε επίπεδο chip. Η διαδικασία αποκόλλησης, τοποθέτησης και συγκόλλησης είναι αυτόματη.

• Η ακριβής ευθυγράμμιση κάθε άρθρωσης συγκόλλησης μπορεί να εγγυηθεί με κάμερα CCD οπτικής ευθυγράμμισης.

•Μπορεί να εξασφαλιστεί ακριβής έλεγχος θερμοκρασίας με 3 ανεξάρτητες περιοχές θέρμανσης. Το μηχάνημα μπορεί να ρυθμίσει και να αποθηκεύσει

1 εκατομμύριο προφίλ θερμοκρασίας.

• Ενσωματωμένη αναρρόφηση στην κεφαλή τοποθέτησης που παίρνει αυτόματα τσιπ BGA μετά την ολοκλήρωση της αποκόλλησης.

3.Προδιαγραφές Auto Optical BGA Rework Station

4.Λεπτομέρειες Auto Optical BGA Rework Station

Κάμερα CCD (σύστημα ακριβούς οπτικής ευθυγράμμισης) ; 2. Ψηφιακή οθόνη HD. 3. Μικρόμετρο (ρυθμίστε τη γωνία του τσιπ) ;

4.3 ανεξάρτητες θερμάστρες (ζεστός αέρας & υπέρυθρες); 5. Τοποθέτηση με λέιζερ. 6. Διεπαφή οθόνης αφής HD, έλεγχος PLC.

7.Led προβολέας? 8.Έλεγχος joystick .

5. Γιατί να επιλέξετε το Auto Optical BGA Rework Station;

6.Πιστοποιητικό Auto Optical BGA Rework Station

7.Συσκευασία & Αποστολή Auto Optical BGA Rework Station

8.Συχνές ερωτήσεις

Πώς να δοκιμάσετε το τσιπ;

Αρχική δοκιμή τσιπ σε επίπεδο συστήματος

Το SoC βασίζεται σε διεργασίες βαθιάς υπομικρών, επομένως η δοκιμή νέων συσκευών Soc απαιτεί μια εντελώς νέα προσέγγιση. Επειδή κάθε λειτουργικό στοιχείο

έχει τις δικές του απαιτήσεις δοκιμών, ο μηχανικός σχεδιασμού πρέπει να κάνει ένα σχέδιο δοκιμής νωρίς στη διαδικασία σχεδιασμού.

Το σχέδιο δοκιμών μπλοκ προς μπλοκ για συσκευές SoC πρέπει να εφαρμοστεί: σωστά διαμορφωμένα εργαλεία ATPG για λογικές δοκιμές. σύντομοι χρόνοι δοκιμής. νέα υψηλής ταχύτητας

μοντέλα σφαλμάτων και δοκιμές πολλαπλής μνήμης ή μικρής συστοιχίας. Για τη γραμμή παραγωγής, η διαγνωστική μέθοδος όχι μόνο εντοπίζει το σφάλμα, αλλά και διαχωρίζει το

ελαττωματικός κόμβος από τον κόμβο εργασίας. Επιπλέον, οι τεχνικές πολυπλεξίας δοκιμής θα πρέπει να χρησιμοποιούνται όποτε είναι δυνατόν για εξοικονόμηση χρόνου δοκιμής. Στον τομέα των υψηλών

Οι ενσωματωμένες δοκιμές IC, οι ελεγχόμενες τεχνικές σχεδίασης ATPG και IDDQ διαθέτουν έναν ισχυρό μηχανισμό διαχωρισμού σφαλμάτων.

Άλλες πραγματικές παράμετροι που πρέπει να προγραμματιστούν εκ των προτέρων περιλαμβάνουν τον αριθμό των ακίδων που πρέπει να σαρωθούν και την ποσότητα της μνήμης σε κάθε άκρο της ακίδας.

Οι σαρώσεις ορίων μπορούν να ενσωματωθούν στο SoC, αλλά δεν περιορίζονται σε δοκιμές διασύνδεσης σε πλακέτες ή μονάδες πολλαπλών τσιπ.

Αν και το μέγεθος του τσιπ μειώνεται, ένα τσιπ μπορεί ακόμα να συσκευάσει εκατομμύρια έως 100 εκατομμύρια τρανζίστορ και ο αριθμός των λειτουργιών δοκιμής έχει αυξηθεί σε πρωτοφανή

επίπεδα, με αποτέλεσμα μεγαλύτερους κύκλους δοκιμών. Αυτό το πρόβλημα μπορεί να δοκιμαστεί. Λειτουργία συμπίεσης για επίλυση, ο λόγος συμπίεσης μπορεί να φτάσει το 20 τοις εκατό έως το 60 τοις εκατό. Για τη σημερινή μεγάλης κλίμακας

σχεδιασμός τσιπ, προκειμένου να αποφευχθούν προβλήματα χωρητικότητας, είναι απαραίτητο να βρεθεί λογισμικό δοκιμής που μπορεί να εκτελεστεί σε λειτουργικά συστήματα 64-bit.

Επιπλέον, το λογισμικό δοκιμής αντιμετωπίζει νέα προβλήματα δοκιμών που προκαλούνται από διεργασίες βαθιάς υπομικρομετρίας και αυξανόμενη συχνότητα. Στο παρελθόν, η λειτουργία δοκιμής ATPG για

ο έλεγχος σφαλμάτων στατικού μπλοκαρίσματος δεν ήταν πλέον εφαρμόσιμος. Η προσθήκη λειτουργικών μοτίβων στα παραδοσιακά εργαλεία κατέστησε δύσκολη την εύρεση νέων σφαλμάτων. Μια καλύτερη προσέγγιση είναι να

ταξινομήστε προηγούμενες ομάδες λειτουργικών λειτουργιών για να προσδιορίσετε ποια σφάλματα δεν μπορούν να εντοπιστούν και, στη συνέχεια, δημιουργήστε μια λειτουργία ATPG για να καταγράψετε αυτούς τους τύπους σφαλμάτων που λείπουν.

Καθώς η χωρητικότητα σχεδιασμού αυξάνεται και ο χρόνος δοκιμής ανά τρανζίστορ μειώνεται, προκειμένου να βρεθούν προβλήματα που σχετίζονται με την ταχύτητα και να επαληθευτεί ο χρονισμός του κυκλώματος, μια σύγχρονη μέθοδος δοκιμής

πρέπει να απασχοληθούν. Οι σύγχρονες δοκιμές πρέπει να ενσωματώνουν πολλαπλά μοντέλα σφαλμάτων, συμπεριλαμβανομένων των παροδικών μοντέλων, των καθυστερήσεων διαδρομής και του IDDQ.

Ορισμένες εταιρείες του κλάδου πιστεύουν ότι ο συνδυασμός σφαλμάτων αποκλεισμού, λειτουργικών και παροδικών σφαλμάτων/καθυστέρησης διαδρομής μπορεί να είναι η πιο αποτελεσματική στρατηγική δοκιμής. Για βαθιά

Τα τσιπ υπομικρών και η λειτουργία υψηλής συχνότητας, η δοκιμή παροδικής και καθυστέρησης διαδρομής είναι ακόμη πιο σημαντικά.

Για να λυθεί το πρόβλημα της ακρίβειας ATE κατά το συγχρονισμό του πυρήνα δοκιμής και να μειωθεί το κόστος, είναι απαραίτητο να βρεθεί μια νέα μέθοδος που να απλοποιεί τη διεπαφή του

τη συσκευή δοκιμής (η δοκιμή μεταβατικής και καθυστέρησης διαδρομής απαιτεί ακριβές ρολόι στη διεπαφή της συσκευής δοκιμής), Διασφαλίζει ότι το σήμα είναι αρκετά ακριβές κατά τη διάρκεια της δοκιμής.

Εφόσον υπάρχει μεγάλη πιθανότητα δημιουργίας ελαττωμάτων στο μπλοκ μνήμης SoC, η μνήμη BIST πρέπει να έχει διαγνωστική λειτουργία. Μόλις εντοπιστεί ένα πρόβλημα,

η ελαττωματική μονάδα διεύθυνσης μπορεί να αντιστοιχιστεί στην πλεονάζουσα μνήμη της εφεδρικής μονάδας διευθύνσεων και η εντοπισμένη διεύθυνση σφάλματος θα απορριφθεί. Αποφύγετε την απόρριψη

ολόκληρο το ακριβό τσιπ.

Η δοκιμή μικρών μπλοκ ενσωματωμένης μνήμης εξαλείφει την ανάγκη για πρόσθετες πύλες ή λογική ελέγχου. Για παράδειγμα, οι τεχνικές δοκιμής μετατροπής διανυσμάτων μπορούν να μετατρέψουν

λειτουργικές λειτουργίες σε μια σειρά από λειτουργίες σάρωσης.

Σε αντίθεση με τη μέθοδο BIST, η λειτουργική είσοδος του μπλοκ μνήμης παράκαμψης δεν απαιτεί πρόσθετη λογική. Επειδή δεν απαιτείται πρόσθετη λογική δοκιμής, SoC

Οι μηχανικοί ανάπτυξης μπορούν να επαναχρησιμοποιήσουν πρότυπα δοκιμών που διαμορφώθηκαν στο παρελθόν.

Τα προηγμένα εργαλεία ATPG όχι μόνο δοκιμάζουν τις μακροεντολές παράλληλα, αλλά καθορίζουν επίσης εάν υπάρχουν διενέξεις, καθώς και λεπτομερώς ποιες μακροεντολές μπορούν να δοκιμαστούν παράλληλα και ποιες

Οι μακροεντολές δεν μπορούν να δοκιμαστούν παράλληλα. Επιπλέον, αυτές οι μακροεντολές μπορούν να δοκιμαστούν αποτελεσματικά ακόμα και αν το ρολόι της μακροεντολής είναι το ίδιο με το ρολόι σάρωσης (όπως η σύγχρονη μνήμη).

Προς το παρόν, δεν υπάρχουν αρκετά σημεία δοκιμής στην πυκνή πλακέτα διπλής όψης και κάθε σύνθετο τσιπ πρέπει να είναι εξοπλισμένο με κύκλωμα σάρωσης ορίων. Χωρίς

Οι σαρώσεις ορίων, οι αναζητήσεις κατασκευαστικών ελαττωμάτων σε επίπεδο πλακέτας είναι αρκετά δύσκολες και δεν μπορούν καν να βρεθούν. Με τη σάρωση ορίων, η δοκιμή σε επίπεδο πλακέτας είναι εξαιρετικά εύκολη

και ανεξάρτητα από το λογικό κύκλωμα μέσα στο τσιπ. Η σάρωση ορίων μπορεί επίσης να διαμορφώσει τη λειτουργία ATPG στην αλυσίδα σάρωσης του τσιπ σε οποιοδήποτε στάδιο της παραγωγής.